Demo

[8] High-bandwidth memory

We use high-bandwidth memory (3D-chip) for quantum simulation task

Check the paper for more information.

[7] Median filter accelerator

We accelerate the median filter, because of demos & study purpose, the hardware design is not effective. [source code].

Check the video demo for more information:

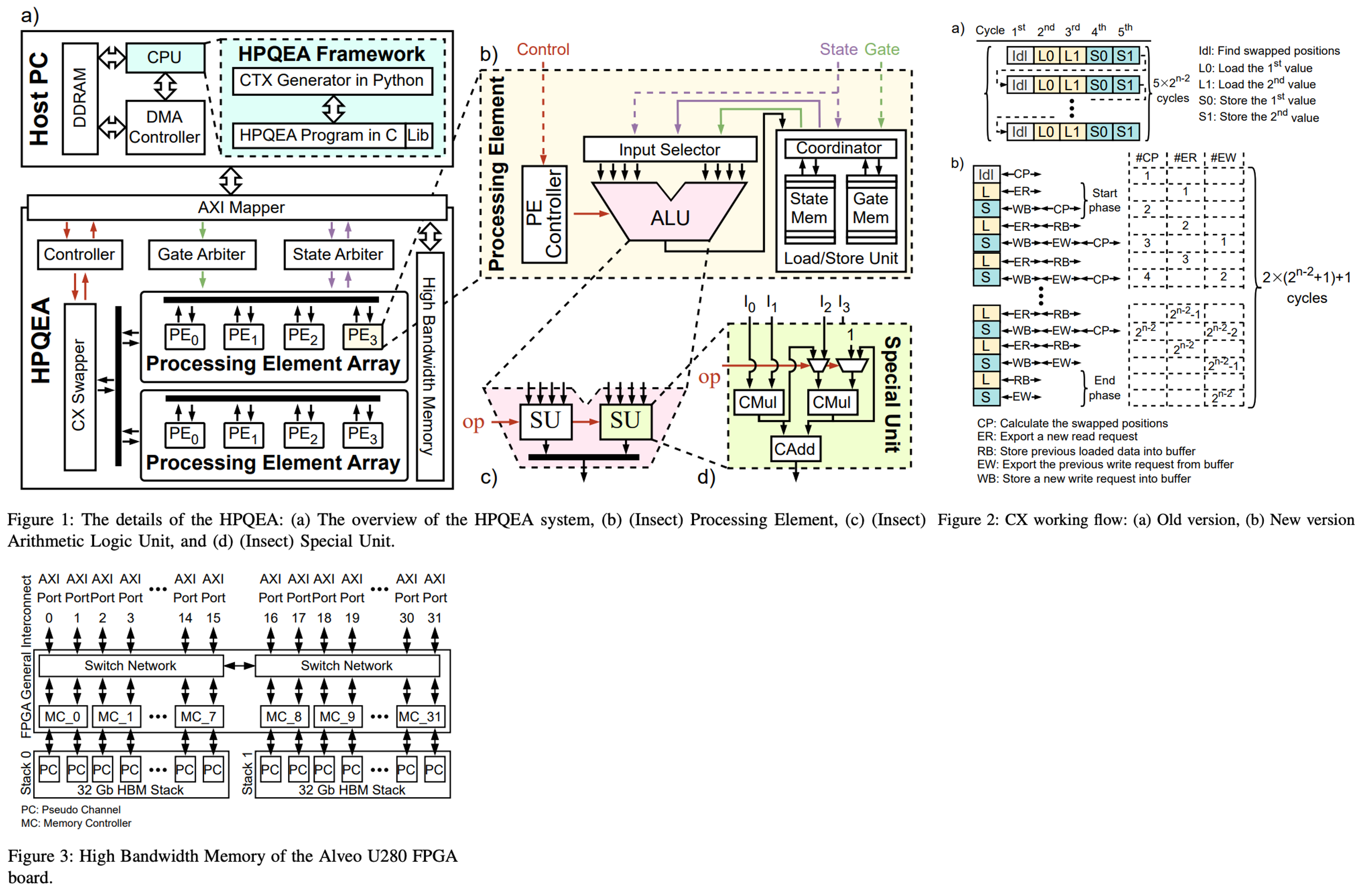

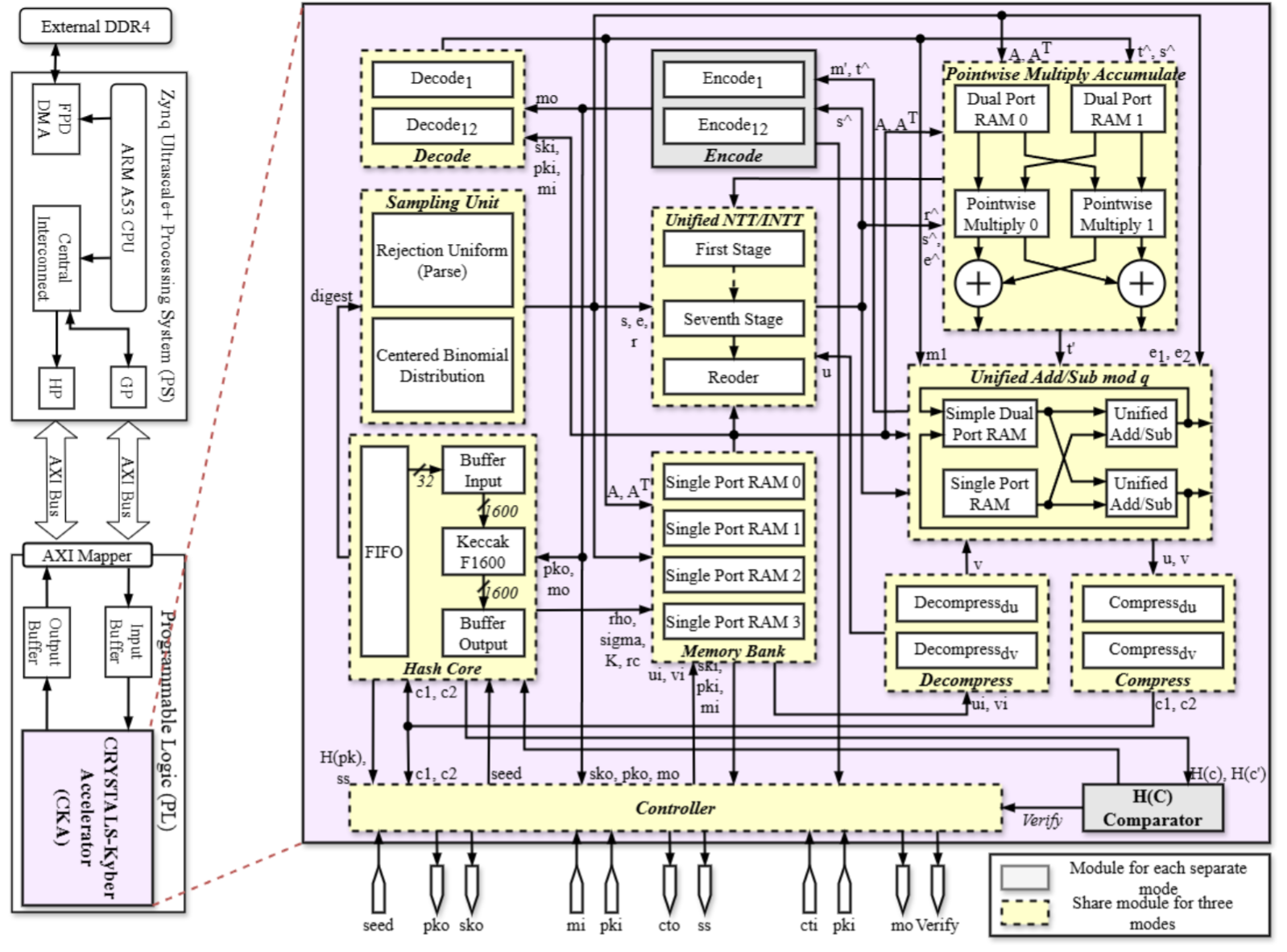

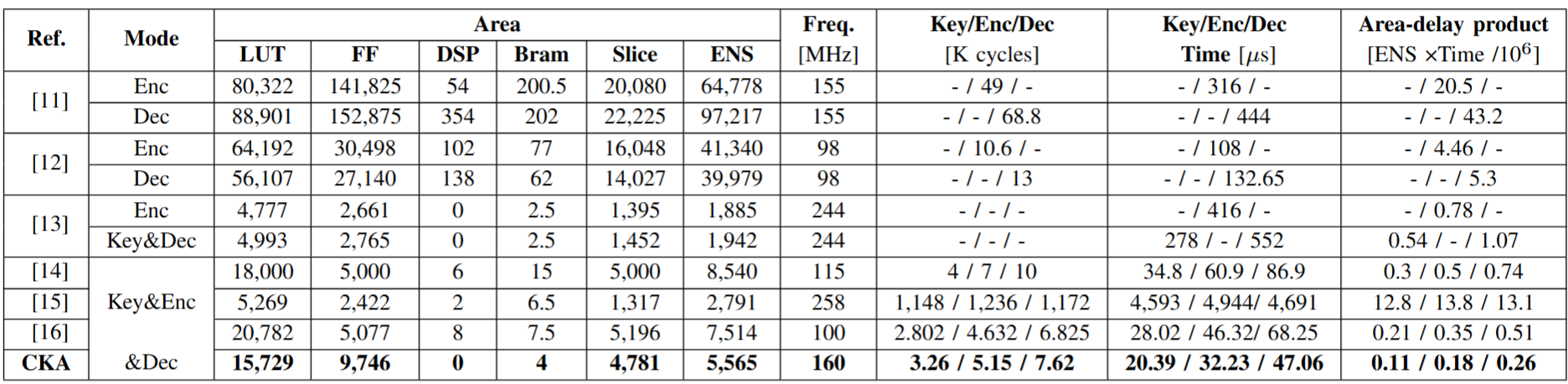

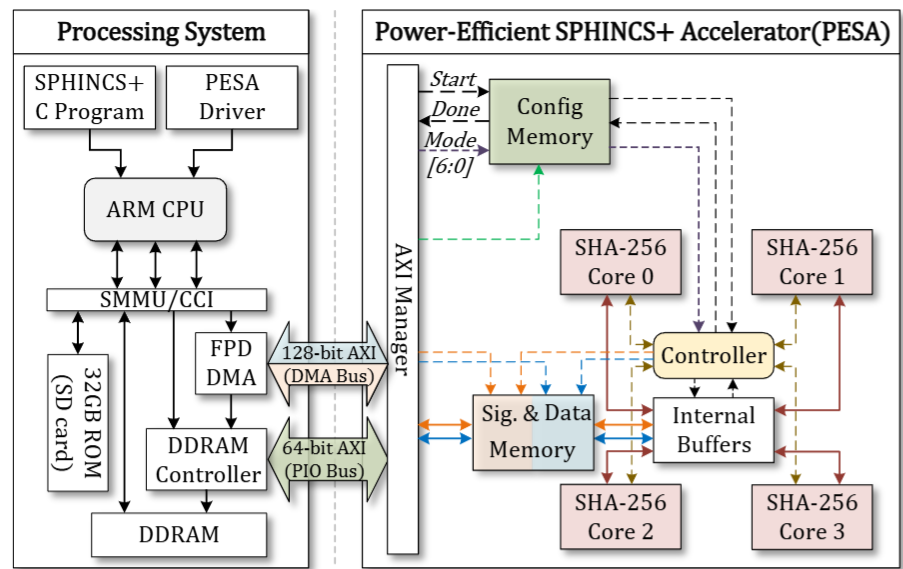

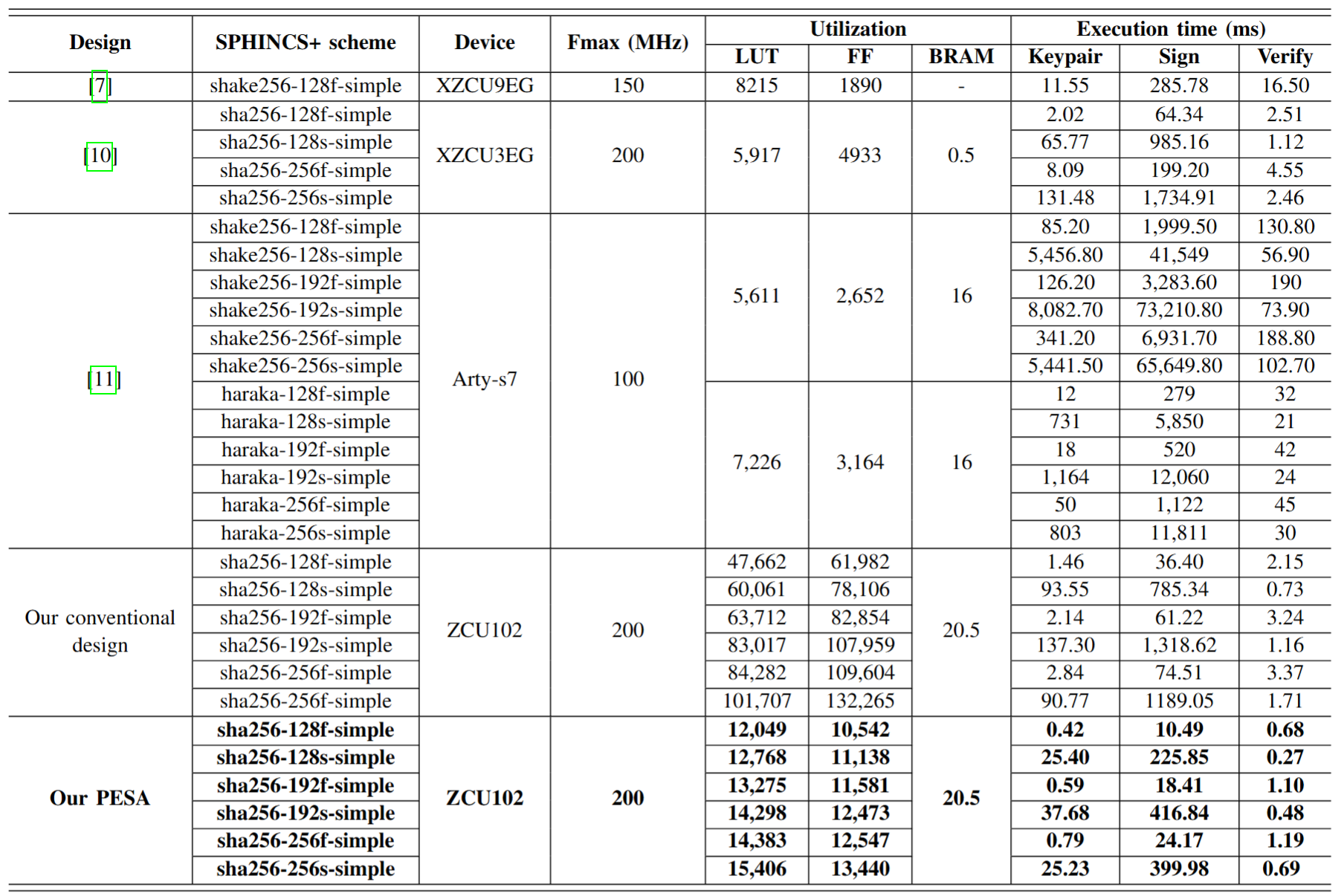

[6] Post-quantum cryptography accelerator

We accelerated Kyber, SPHINCS+ (FALCON in progress) [link1] [link2].

Figure 6.1. Kyber accelerator archtecture.

Figure 6.2. Hardware implementation evaluation and comparisons.

Figure 6.3. SPHINCS+ accelerator archtecture.

Figure 6.4. Hardware implementation evaluation and comparisons.

Check the video demo for more information:

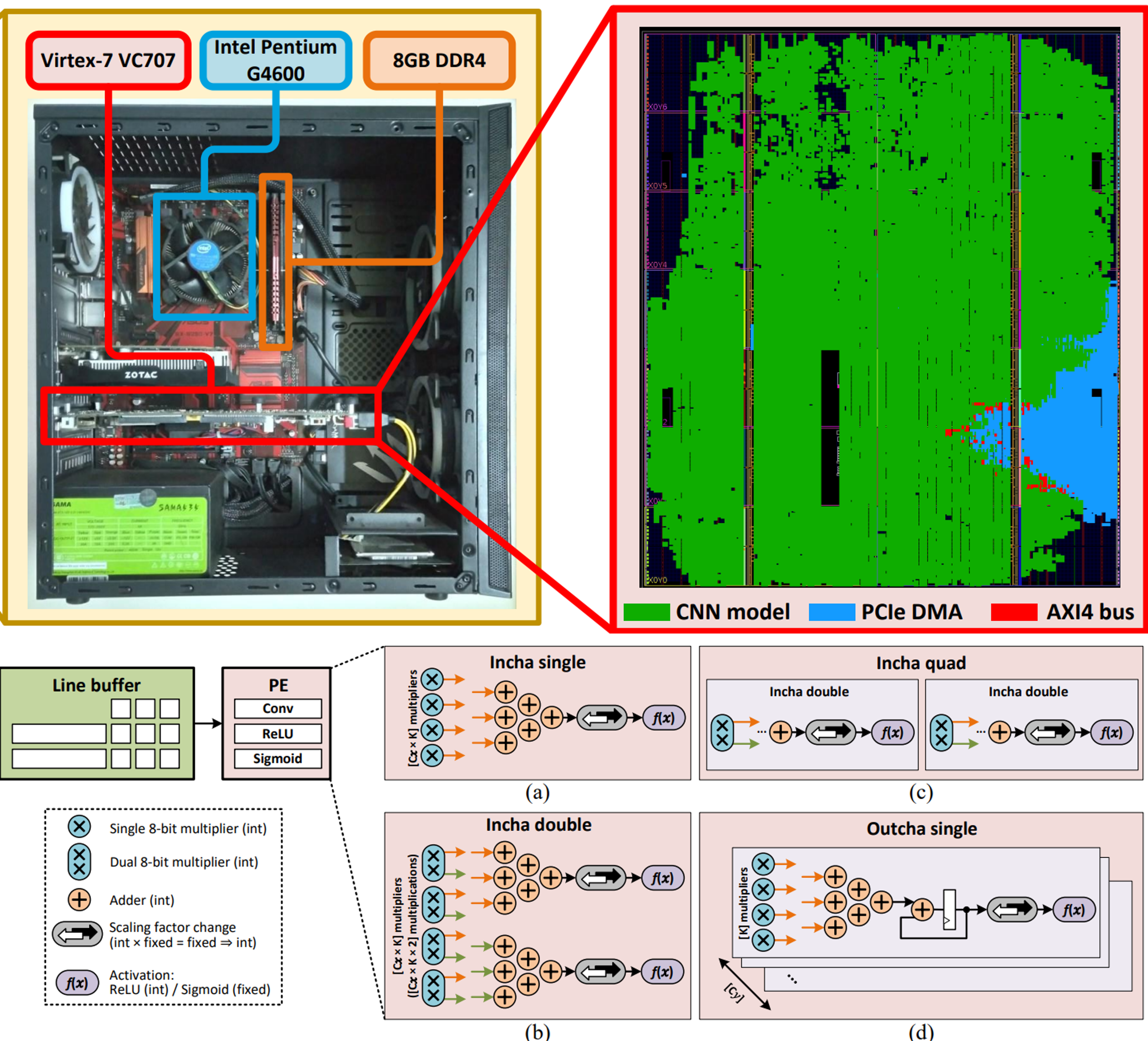

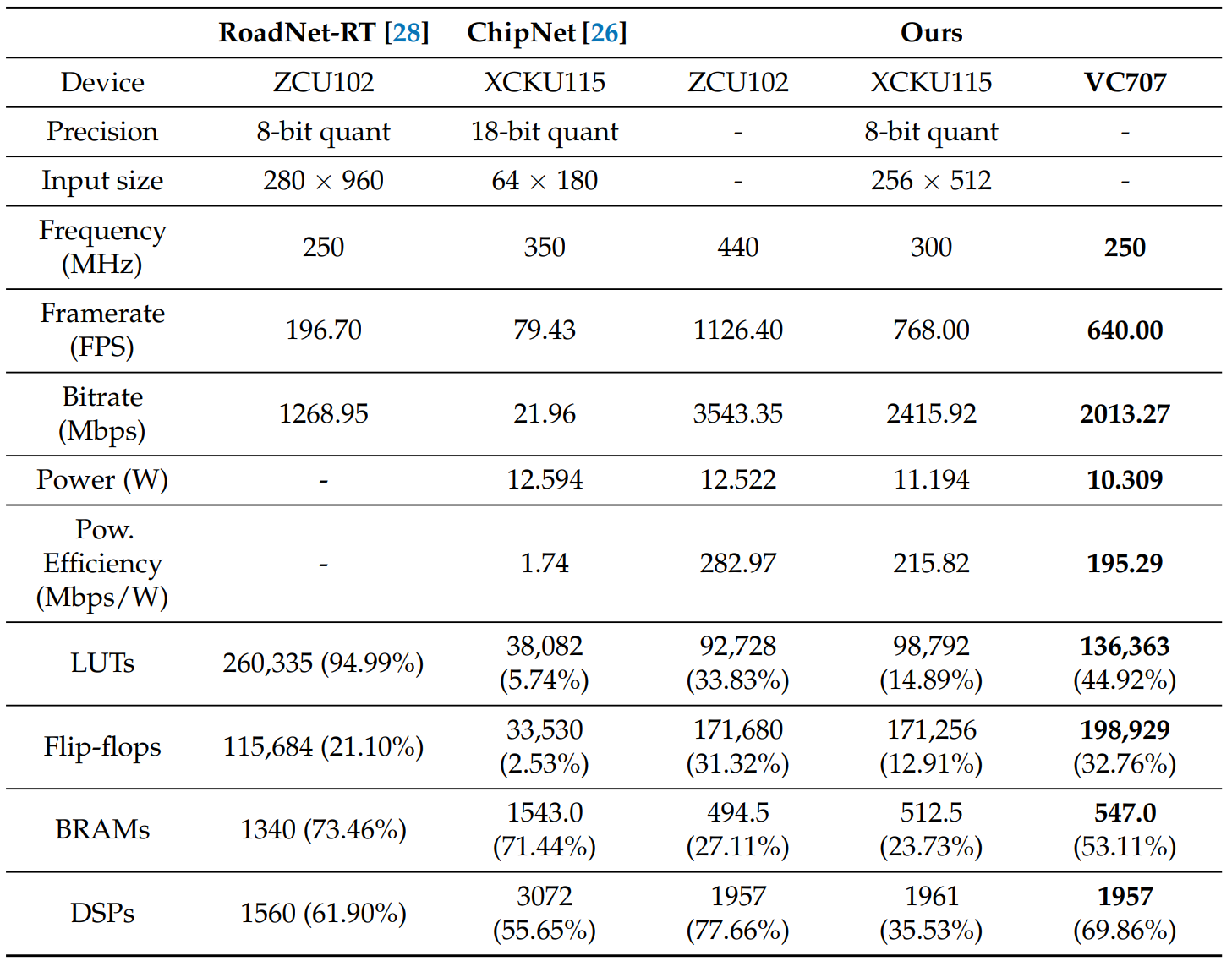

[5] Lane detection accelerator for auto-car

This accelerator can achieved up to 640 FPS [code].

Figure 5.1. Full system operation, including results captured on monitor, and Floorplan of the FPGA chip.

Figure 5.2. Hardware implementation evaluation and comparisons.

Check the video demo for more information:

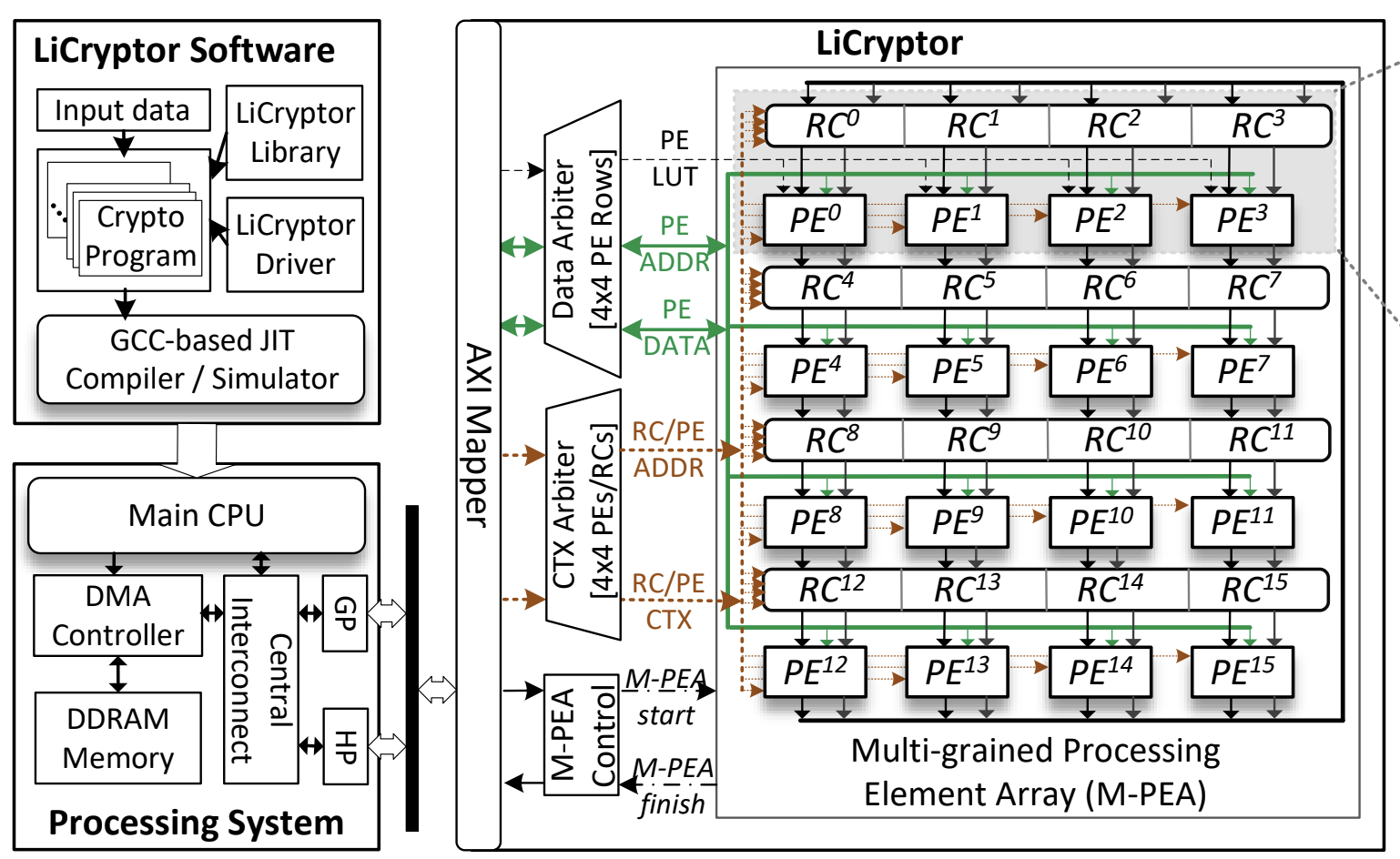

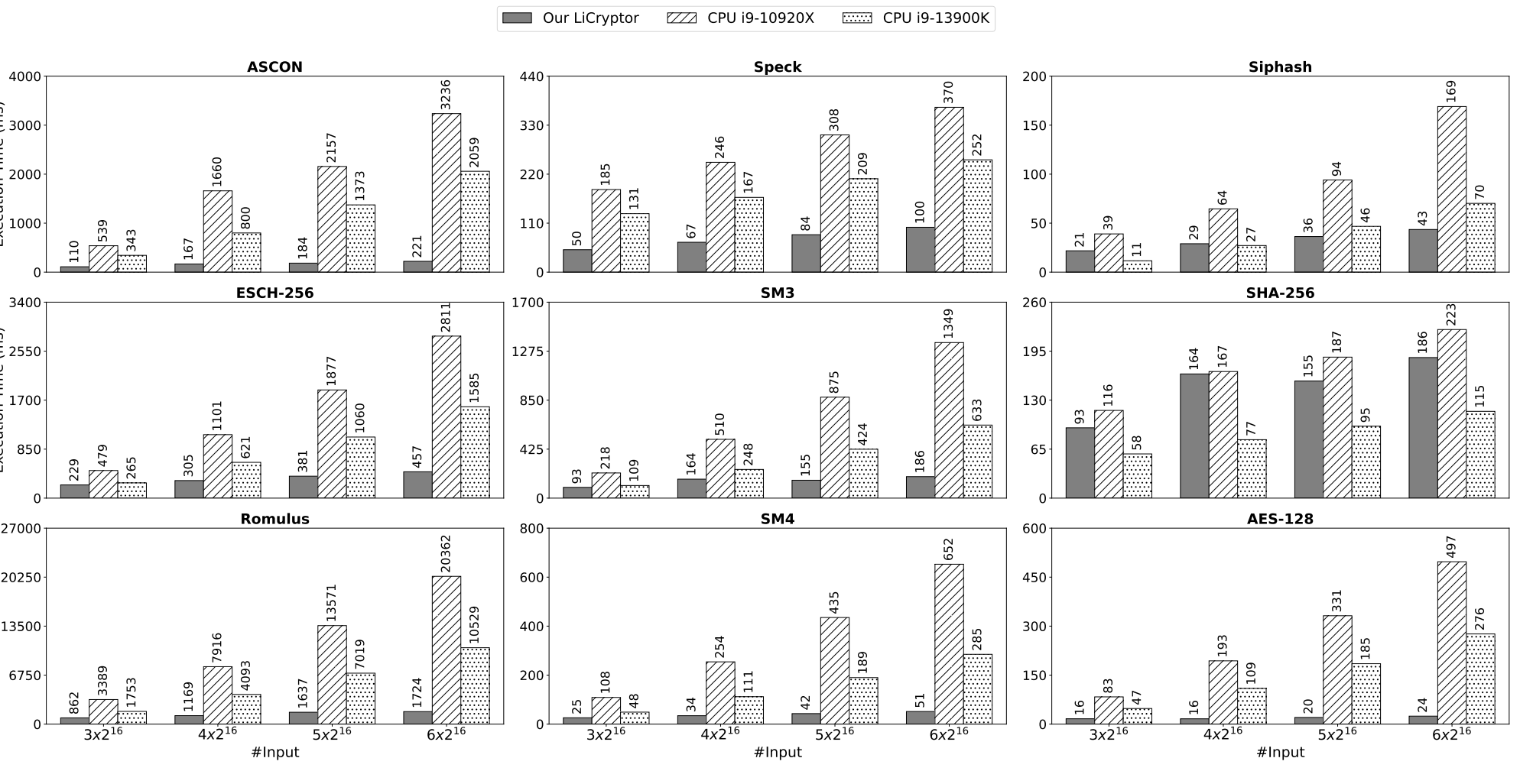

[4] CRGA for cryptography

We apply CRGA architecture for various popular cryptography

Scientific paper (pre-print): [link1] [pdf1] [link2] [pdf2] [link3] [pdf3] [code]

Figure 4.1. LiCryptor overview architecture at the SoC level.

Figure 4.2. Execution times of our LiCryptor and two powerful CPUs for 64-bit, 32-bit, and 8-bit LWC algorithms.

Check the video demo for more information:

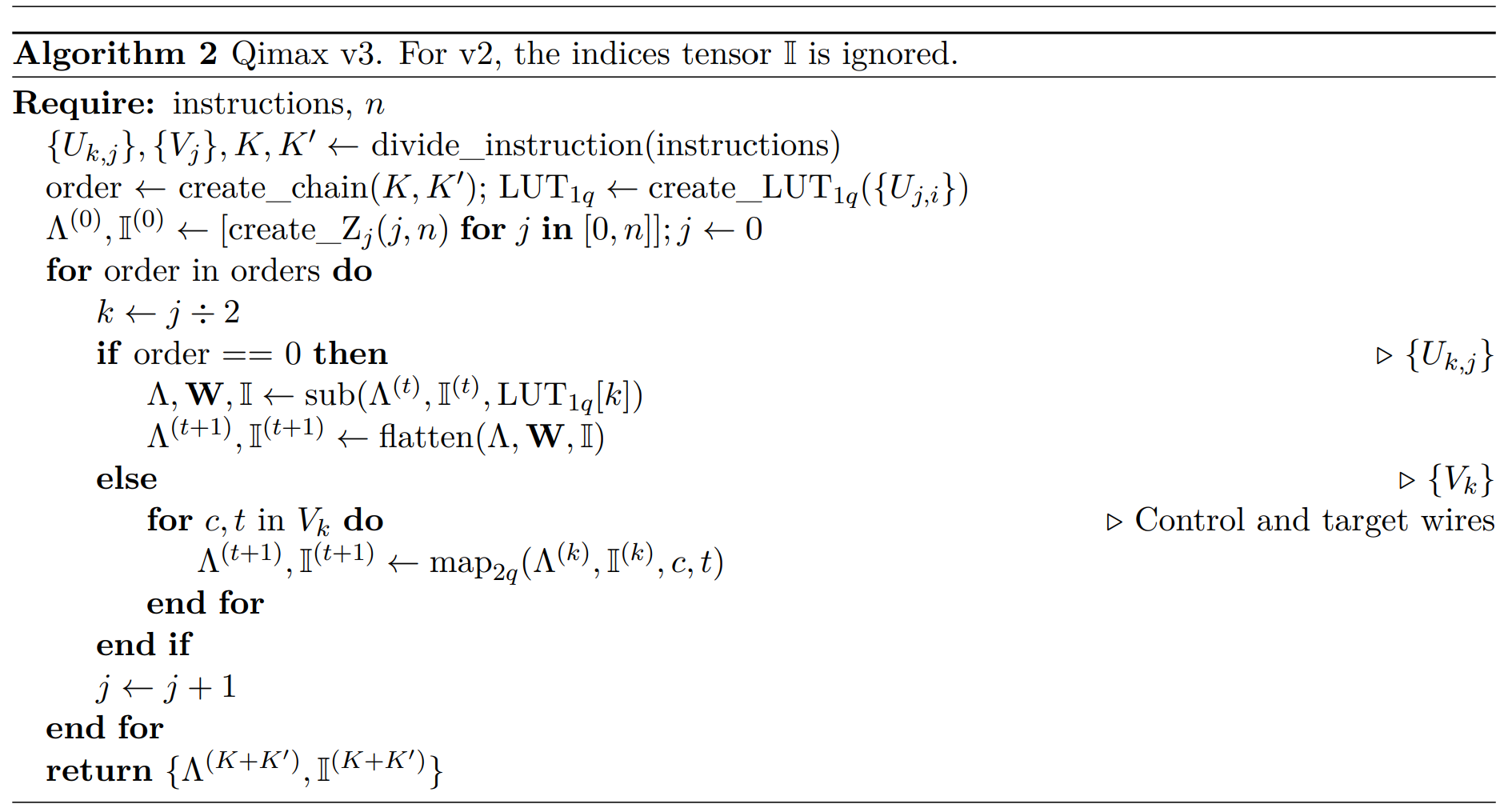

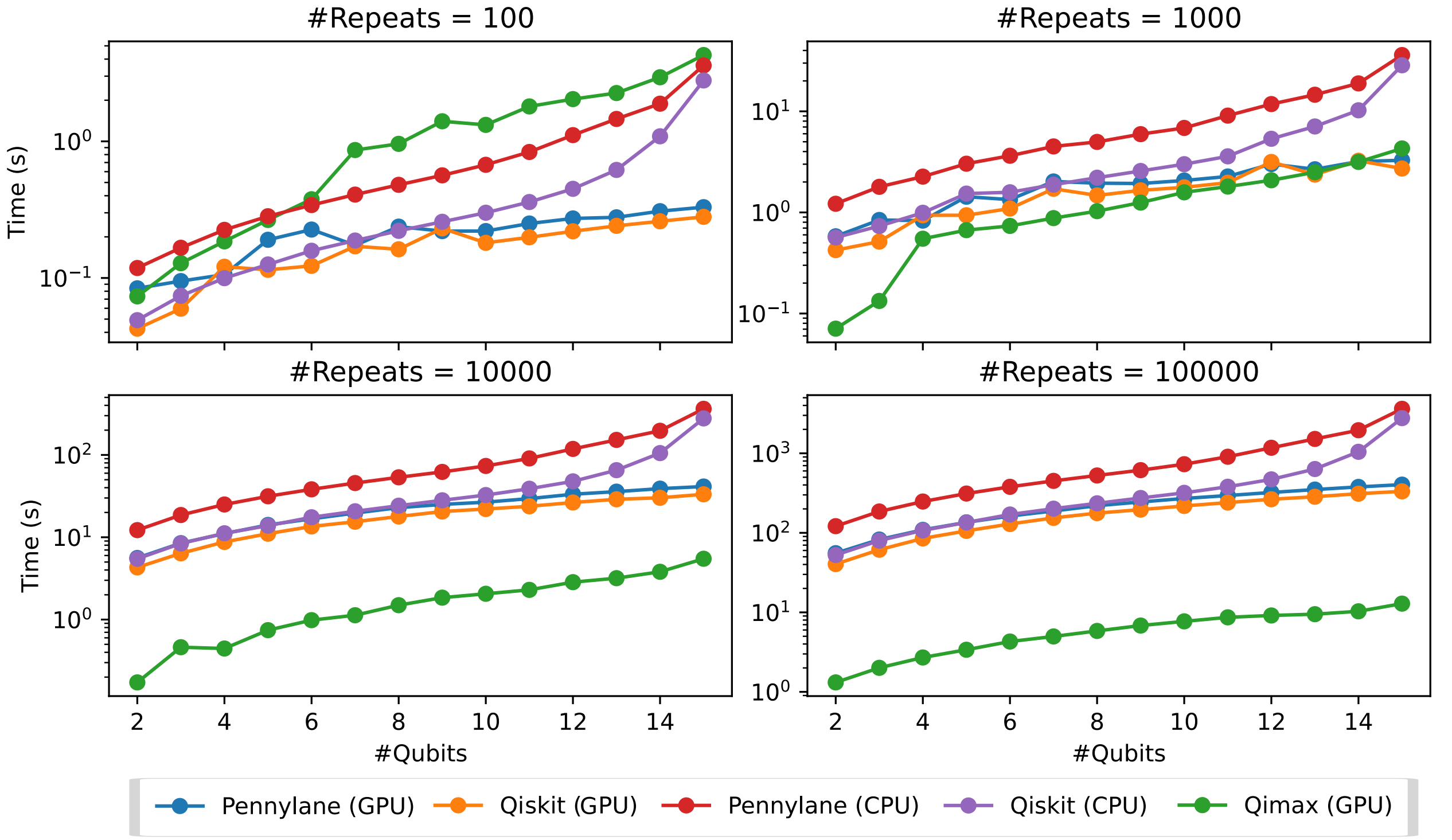

[3] Qimax: A parallel stabilizer formalism package

Qimax is a parallel stabilizer pakcage which is used for simulating both Clifford and non-Clifford circuit.

Scientific paper (pre-print): [link] [pdf] [code]

Figure 3.1. Qimax v3. For v2, the indices tensor I is ignored.

Figure 3.2. Execution time from different versions of Pennylane, Qiskit, and Qimax. The y-axis is plotted on logarithmic scale. The range of #Qubits is 2 to 15.

[2] FQsun: A wave-function based emulator

We use FPGA ZCU102 to emulate a (up to 30 qubits) quantum system, based on state-vector (wave-function variant).

Scientific paper (ACCESS): [link] [pdf] [code]

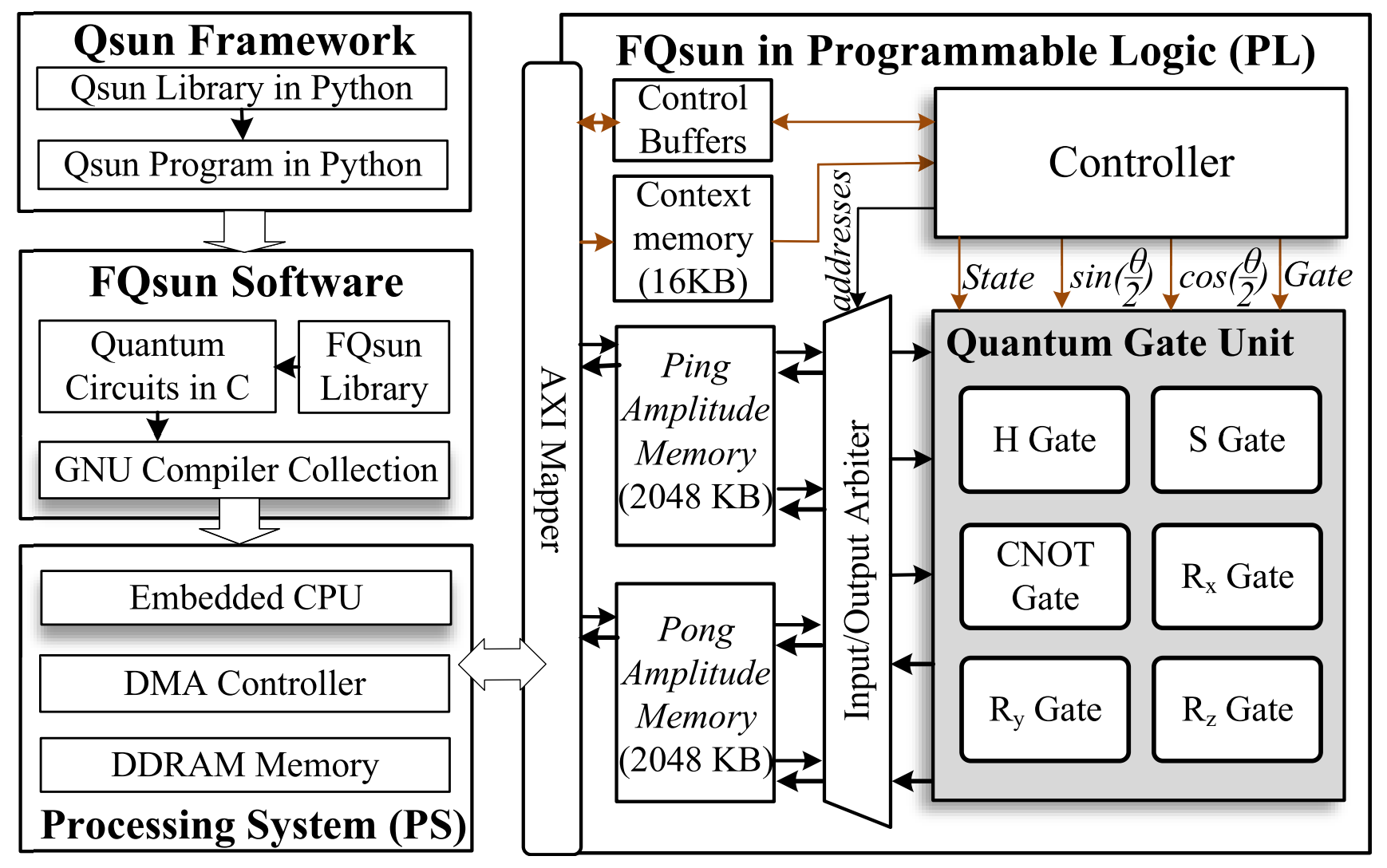

Figure 2.1. Overview architecture of our FQsun at the system-on-chip (Soc) level on FPGA. The arrow stands for dataflow. FQsun in PL communicates with PS through AXI Mapper and DMA Controller.

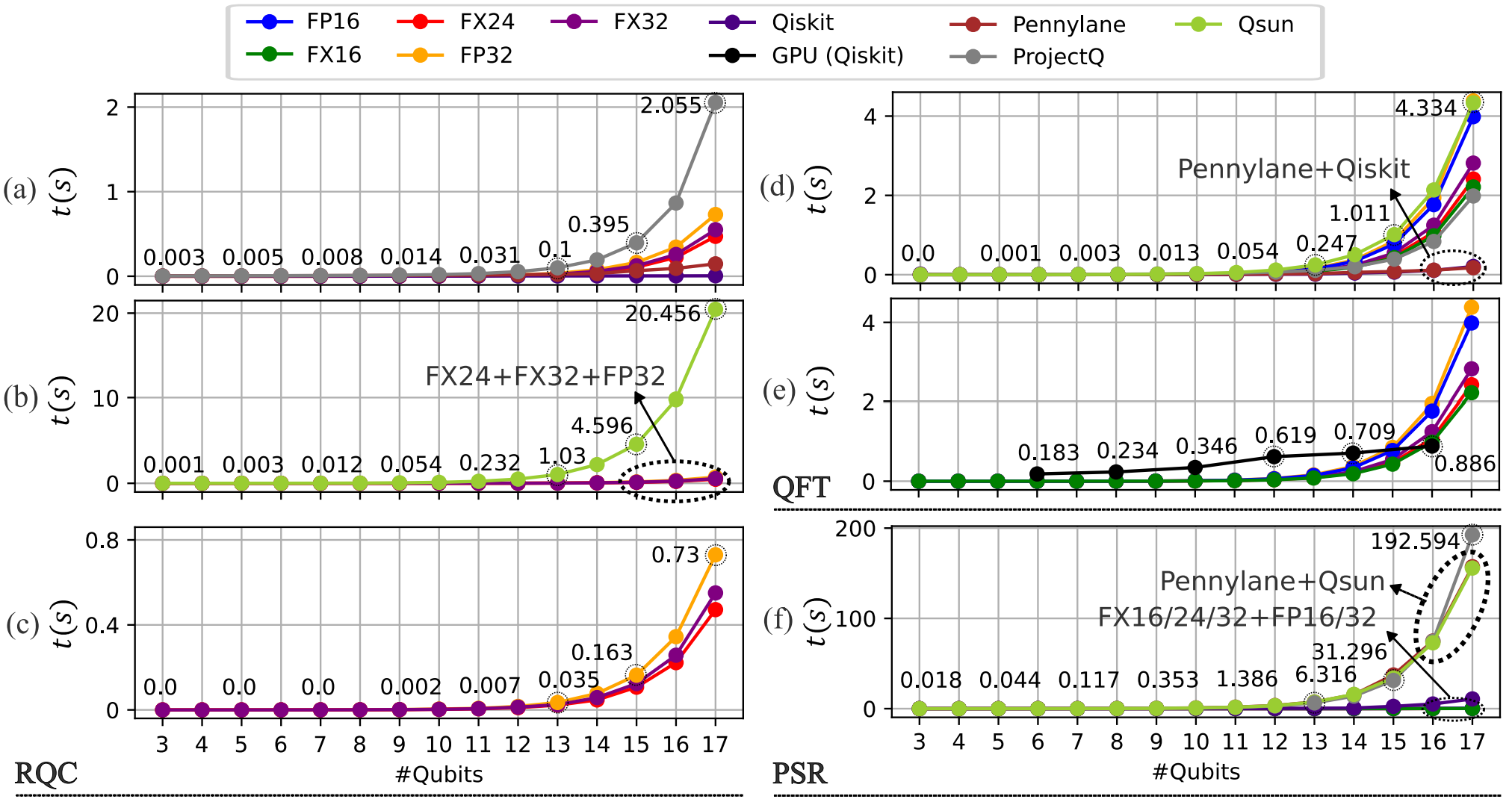

Figure 2.2. The execution time comparison

Check the video demo for more information:

[1] ECG processing for medical application

We propose a 1D-CNN accelerate (MINA) for processing ECG signal series for detecting heart disease.

Scientific paper (TCAS-I): [link] [pdf] [code]

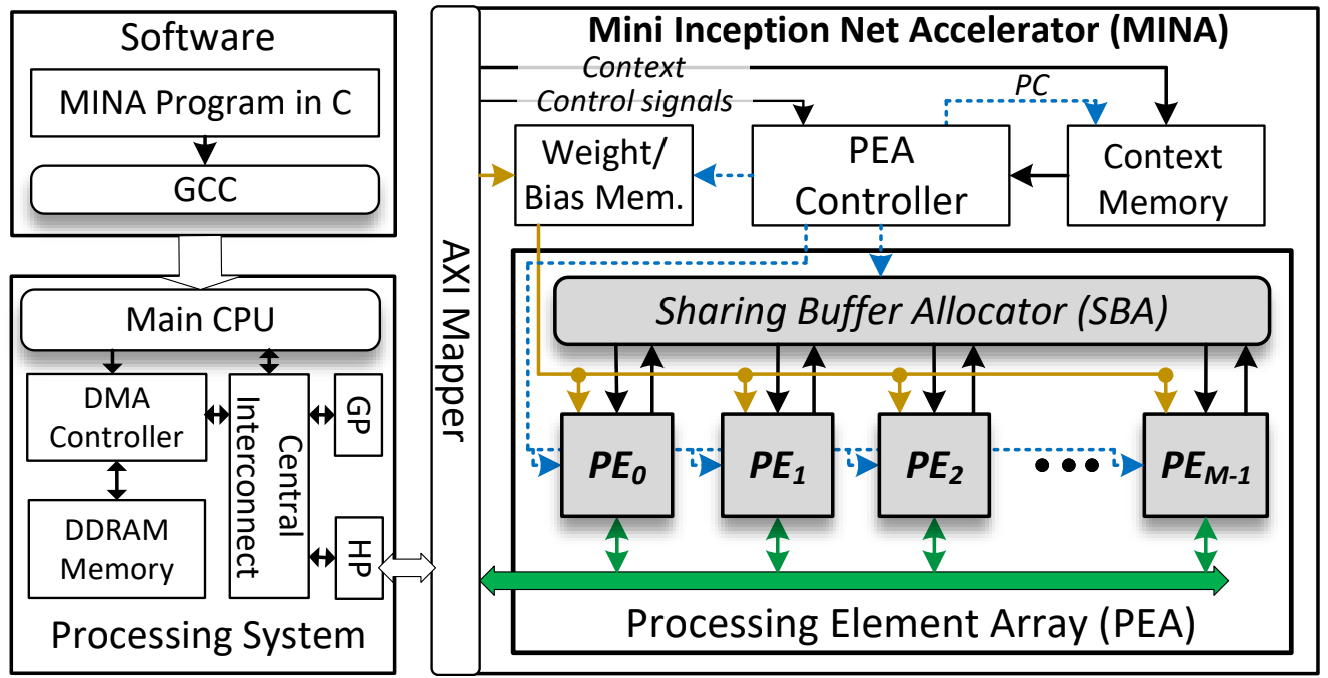

Figure 1.1. MINA overview architecture

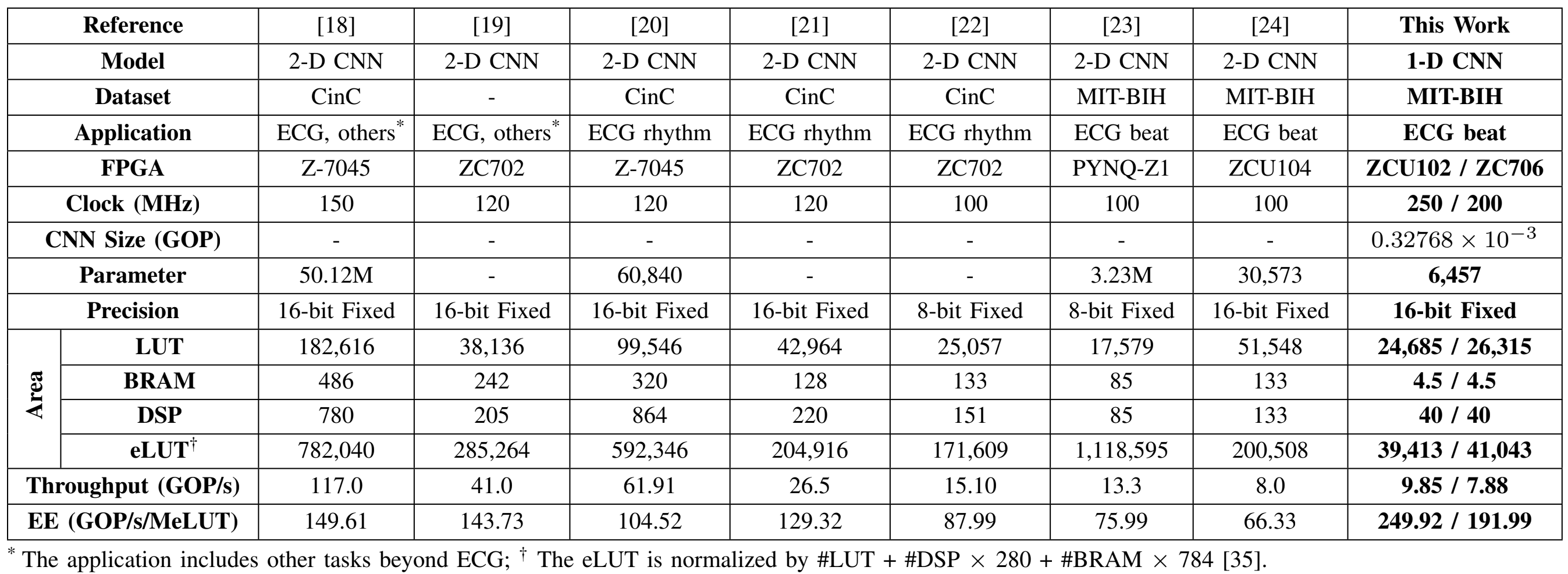

Figure 1.2. Comparison with fpga-based 2-d cnn hardware architectures for ecg classification.

Check the video demo for more information: